Research Projects

High energy-efficiency data converters

The goal of this research is to develop ring oscillator (RO) based mostly-digital ADCs with high energy efficiency. We are also interested in applying machine learning techniques to improve performance of data converters in advanced processes as well as building cognitive radios. Some of our on-going and prior research efforts are below:

a. Digital phase-locked loop (DPLL) based second-order delta-sigma:

A modified digital phase-locked loop (DPLL) architecture is used for the proposed ADC design. The analog input perturbs the digitally controlled oscillator (DCO) phase and the DPLL changes the DCO control word to cancel out the phase perturbation. Thus, the DCO control word acts as a quantized representation of the analog input. Ring oscillators are used as DCO and DPLL loop filter, resulting in highly digital architecture and high-order quantization noise shaping. The merits of the proposed ADC are a) no nonlinearity calibration b) excess loop delay can be compensated without requiring auxiliary DAC c) inherent DAC mismatch shaping.

A modified digital phase-locked loop (DPLL) architecture is used for the proposed ADC design. The analog input perturbs the digitally controlled oscillator (DCO) phase and the DPLL changes the DCO control word to cancel out the phase perturbation. Thus, the DCO control word acts as a quantized representation of the analog input. Ring oscillators are used as DCO and DPLL loop filter, resulting in highly digital architecture and high-order quantization noise shaping. The merits of the proposed ADC are a) no nonlinearity calibration b) excess loop delay can be compensated without requiring auxiliary DAC c) inherent DAC mismatch shaping.

Collaborators: Dr. Abhijit Das (TI)

Funding support: Semiconductor Research Corporation (SRC)

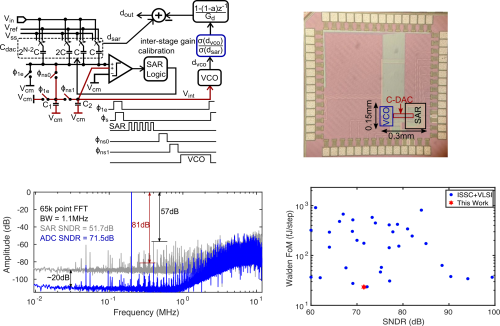

b. Noise-shaping SAR+VCO ADC:

The key contribution of this work is to address the challenge of driving large sampling capacitor for high resolution noise-shaping successive approximation register (NS-SAR) ADC. The proposed architecture reduces resolution of SAR stage and leverages residue attenuation due to passive charge sharing in the NS SAR to linearize the VCO. Combining an NS SAR with a VCO ADC shapes in-band thermal noise of VCO and SAR comparator at ADC output.

The key contribution of this work is to address the challenge of driving large sampling capacitor for high resolution noise-shaping successive approximation register (NS-SAR) ADC. The proposed architecture reduces resolution of SAR stage and leverages residue attenuation due to passive charge sharing in the NS SAR to linearize the VCO. Combining an NS SAR with a VCO ADC shapes in-band thermal noise of VCO and SAR comparator at ADC output.

Collaborators: Dr. Stefano Pietri (NXP)

Wearable AI for at-home precision healthcare

The goal of this research is to develop smart wearables that will perform in-sensor AI analysis on user physiological signals, and perform fusion with electronic medical/healthcare records (EMR/EHR) for precision and personalized healthcare. In-sensor processing reduces latency and transmission energy, and improves security of patient data. We design analog in-memory computing neural networks and reservoir computing based recurrent neural networks for in-sensor AI computation at tens of nano-joule/inference. We are developing novel in-memory computing SRAM macros with very high linearity and dynamic input/weight precision.

The goal of this research is to develop smart wearables that will perform in-sensor AI analysis on user physiological signals, and perform fusion with electronic medical/healthcare records (EMR/EHR) for precision and personalized healthcare. In-sensor processing reduces latency and transmission energy, and improves security of patient data. We design analog in-memory computing neural networks and reservoir computing based recurrent neural networks for in-sensor AI computation at tens of nano-joule/inference. We are developing novel in-memory computing SRAM macros with very high linearity and dynamic input/weight precision.

We have fabricated several IC prototypes to detect atrial fibrillation, sepsis and stress from patient ECG signal and fusion with their EMR data.

Funding support: Air Force Research Labs/ Nano-bio materials consortium/ SEMI, National Science Foundation (NSF)

Funding support: Air Force Research Labs/ Nano-bio materials consortium/ SEMI, National Science Foundation (NSF)

Collaborators: Prof. Imon Banerjee (Mayo Clinic/ASU), Prof. Jung-Hun Seo (UB SUNY), Prof. Neal Bhatia (Emory University)

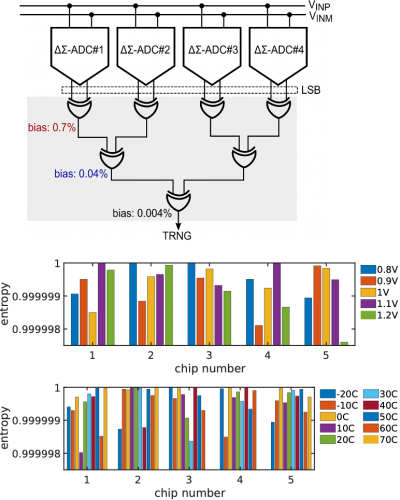

Hardware Security

a. True-random number generator and physical unclonable functions: We are developing silicon true-random number generators (TRNGs) and physical unclonable functions (PUFs) using entropy sources available in ADCs (thermal noise for TRNGs, mismatch for PUFs).

a. True-random number generator and physical unclonable functions: We are developing silicon true-random number generators (TRNGs) and physical unclonable functions (PUFs) using entropy sources available in ADCs (thermal noise for TRNGs, mismatch for PUFs).

Funding support: Semiconductor Research Corporation (SRC)

b. On-chip solutions for malware detection: We are developing ultra-low energy, on-chip mixed-signal recurrent neural networks for malware detection from hardware performance counters (HPCs) which are built-in in most modern processors.

Collaborator: Prof. Kanad Basu (UT Dallas)

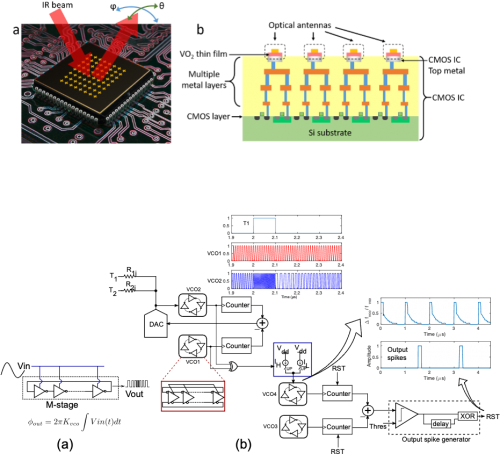

Dynamic optical phased array (DOPA) and LIDAR

In this project, we plan to develop a high antenna-density scalable on-chip DOPA architecture employing a metasurface-like tunable optical antenna array directly integrated on a CMOS chip of custom-designed control circuits. The proposed DOPA architecture is designed for steering (or performing other manipulations of) a free-space incident light beam, and is thus more versatile than waveguide-based DOPA architectures which are limited to light supported by waveguide modes. Each tunable optical antenna element consists of a thin film based on phase-change element that forms patch antenna structure. Tuning of the antenna optical phase is achieved by inducing insulator-to-metal transition by applying a voltage between the metal back-plate and the top metal patch.

In this project, we plan to develop a high antenna-density scalable on-chip DOPA architecture employing a metasurface-like tunable optical antenna array directly integrated on a CMOS chip of custom-designed control circuits. The proposed DOPA architecture is designed for steering (or performing other manipulations of) a free-space incident light beam, and is thus more versatile than waveguide-based DOPA architectures which are limited to light supported by waveguide modes. Each tunable optical antenna element consists of a thin film based on phase-change element that forms patch antenna structure. Tuning of the antenna optical phase is achieved by inducing insulator-to-metal transition by applying a voltage between the metal back-plate and the top metal patch.

An application of the proposed DOPA system is for LIDAR. We are developing time-domain, mixed-signal circuits for ultra-low energy spiking neural network that will be an enabler for integration of AI-based image detection capabilities with on-chip DOPA system.

Collaborators: Prof. Peter Qiang Liu (UB SUNY), Prof. Quanxi Jia (UB SUNY), Prof. Xiaohua Li (SUNY Binghampton)