# OTA-free 1-1 MASH ADC using Fully Passive Noise Shaping SAR & VCO ADC

Sanjeev Tannirkulam Chandrasekaran<sup>1</sup>, Sumukh P. Bhanushali<sup>1</sup>, Stefano Pietri<sup>2</sup> and Arindam Sanyal<sup>1</sup> <sup>1</sup>University at Buffalo, Buffalo, NY; <sup>2</sup>NXP Semiconductor, Austin, TX; stannirk@buffalo.edu

#### Abstract

We present an OTA-free 1-1 MASH ADC utilizing a fully passive noise shaping (FPNS) SAR as first-stage and openloop VCO ADC as second stage. The key contribution of this work is to address the challenge of driving large sampling capacitor for high resolution NS-SAR. The proposed architecture reduces resolution of SAR stage and leverages residue attenuation due to passive charge sharing in the FPNS SAR to linearize the VCO. Combining an FPNS SAR with a VCO ADC shapes in-band thermal noise of VCO and SAR comparator at ADC output. Additionally, we demonstrate a computationally inexpensive foreground inter-stage gain calibration algorithm for the proposed ADC architecture. The prototype ADC consumes 0.16mW while achieving an SNDR/DR of 71.5/75.8dB over a 1.1MHz bandwidth and walden FoM of 23.3fJ/step which is the lowest in 65nm technology.

**Keywords:** noise-shaping SAR, ring VCO, oversampling ADC, inter-stage gain calibration and MASH

### Introduction

NS-SAR ADCs combine the advantages of both SAR and  $\Delta \Sigma$  and suppresses comparator thermal noise and ADC quantization noise in the signal band. However, state-of-the-art NS-SAR ADCs use 9-11 bit DAC to achieve ~12/13 bit resolution at low OSR, which brings the challenge of driving large sampling capacitor [1-2]. MASH architecture can address this challenge by reducing the sampling capacitor in the first NS-SAR stage. A recent work [3] has presented a 1-2 MASH with NS-SAR ADCs in both stages. The first NS-SAR stage uses active integrator which is re-used to amplify residue of first stage. However, the use of active integrator makes the ADC less scaling friendly and increases overall power consumption of the ADC.

We propose an OTA-free MASH ADC which uses 5-bit FPNS-SAR as first stage and a ring VCO as second stage. The passive integrator output of the SAR stage drives the second stage VCO. Attenuation of passive integrator output due to charge sharing linearizes the VCO for low-resolution SAR which relaxes the driving requirement. Since VCO provides intrinsic amplification, separate inter-stage gain amplification is not needed. We use a fast-convergence digital foreground calibration technique to extract interstage gain precisely.

## **Proposed Architecture**

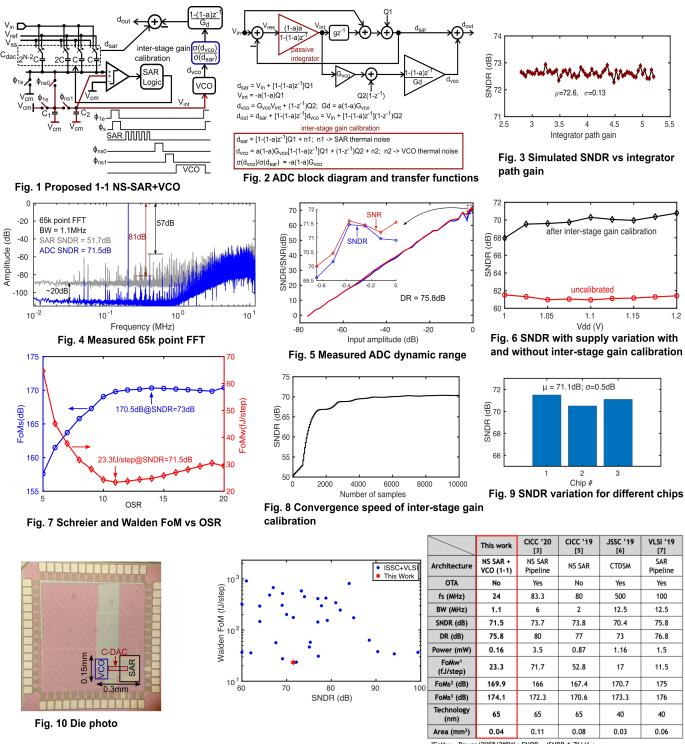

Fig. 1 illustrates the proposed MASH ADC architecture and timing diagram. The FPNS-SAR acts as coarse quantizer, and the second-stage VCO acts as fine quantizer. The SAR residue is first charge-shared with a small capacitor,  $C_1=aCdac/(1-a)$ , during  $\emptyset ns0$ , and then integrated on  $C_2=Cdac$  during  $\emptyset ns1$ cycles. In this design a=0.25, which results in an NTF of (1- $0.75z^{-1}$ ) for the SAR stage. The integrated residue (Vint) is fed to the VCO ADC in the second stage. Fig. 2 shows the block diagram of the proposed ADC and its transfer functions. The SAR stage uses multi-path comparator with the passive integration path having a gain of g=1/a. Quantization noise of the ADC is set by quantization noise in the VCO as well as comparator in the SAR stage are high passed by (1-0.75z<sup>-1</sup>), and the in-band noise floor is set by kT/C noise of the SAR stage, and in particular kT/C noise of C<sub>1</sub>.

The 5-bit SAR uses bi-directional single-sided switching technique to reduce switching energy by 86% compared to the conventional SAR. A PMOS gm-stage converts Vint to current for driving the VCO stage. The VCO stage has 7 inverters in which phase output of all the inverters are read-out to form the VCO output. Fig. 3 shows variation in simulated ADC SNDR as the integration path gain, g, is swept from -30% to 30%. The ADC has very low sensitivity to 'g' which obviates the need for precise matching or calibration.

#### **Inter-stage Gain Calibration**

The inter-stage gain is set by a(1-a)CpGvco where Cp is the attenuation due to parasitic capacitance at the passive integration node, and Gvco is the gain of the VCO stage. Cp and 'a' are set by ratio of capacitors and has low sensitivity to PVT, while Gvco is highly sensitive to PVT. We use Nedler-Mead technique to perform one-time calibration and extract 'a'. and hence, the NTF zero for the SAR stage. To extract Gvco, we use a simple digital calibration technique. As seen from the ADC transfer functions in Fig. 2, if Vin is set to 0, ratio of standard deviation of VCO output to standard deviation of SAR output is a measure of the inter-stage gain. The error in the inter-stage gain calculation is due to thermal noise in SAR and VCO stages and quantization noise Q2 of VCO. Since the SAR has low resolution of 5-bit, its quantization noise Q1 has a larger standard deviation than the other noise components which reduces error in inter-stage extraction. The inter-stage gain calibration needs to be performed with change in VT which can be monitored by observing the VCO frequency over time using a digital counter clocked by 1 inverter in the VCO.

#### **Measurement Results**

The proposed ADC is fabricated in 65nm and consumes 160µW from 1.1V supply at 24MHz sampling frequency. Out of 160µW power, the SAR consumes 110µW and the VCO consumes 50µW. Fig. 4 shows the measured 65k point FFT. The overall ADC has 20dB lower in-band noise floor and 24dB better SFDR than the SAR stage. The ADC has an SNDR of 71.4dB at an OSR of 11. Fig. 5 shows the measured SNR/SNDR versus input amplitude. The ADC has a dynamic range of 75.8dB, and the upper limit on SNR is due to increase in noise floor due to capacitor mismatch which is not calibrated in this design. Fig. 6 shows SNDR with and without inter-stage gain calibration as the supply voltage is swept by +/-10%. Fig. 7 shows walden and schreier FoM vs OSR. Fig. 8 shows convergence speed of the inter-stage gain calibration technique without applying any input signal. The gain calibration requires 5000 samples (0.21ms) for convergence. Fig. 9 shows the SNDR of 3 test-chips. The average SNDR is 71.1dB. The die micro-photograph is shown in Fig. 10. Fig. 11 compares graphically walden FoM of the proposed ADC with state-ofthe-art oversampling ADCs in 65nm, and with state-of-the-art ADCs with similar bandwidth across technology. The proposed ADC achieves the best walden FoM at 65nm, and the ADC performance can be improved further with technology scaling.

Acknowledgment The authors would like to thank Michael

2021 Symposium on VLSI Circuits Digest of Technical Papers

Berens of NXP Semiconductor, Austin, TX for insightful discussions during the ADC design phase.

References

[1] X. Tang, et. al., ISSCC, 2020, pp. 162-164. [2] H. Zhuang, et. al.,

*CICC*, 2020, pp. 1-4. [3] S. Oh, et. al., *CICC*, 2020, pp. 1-4. [4] L. Chen, et. al., *ESSCIRC*, 2014, pp. 219-222. [5] T. Kim, et. al., *CICC*, 2019, pp. 1-4. [6] J. Liu, et. al., *JSSC*, 2019, pp. 428-440. [7] C.-K Hsu, et. al., *VLSI*, 2019, pp. C68-C69.

<sup>1</sup>FoMw = Power/2<sup>ENOB</sup>/2\*BW ; ENOB = (SNDR-1.76)/6 ; <sup>2</sup>FoMs = SNDR + 10\*log10(BW/Power) ; <sup>3</sup>FoMs = DR + 10\*log10(BW/Power)

2 978-4-86348-780-2 ©2021 JSAP

2021 Symposium on VLSI Circuits Digest of Technical Papers

Authorized licensed use limited to: University at Buffalo Libraries. Downloaded on August 09,2021 at 17:05:30 UTC from IEEE Xplore. Restrictions apply.

Fig. 11 Performance comparison with state-of-the-art